- Die Vorlesung baut auf die in den Grundlagen der Rechnerarchitektur und -organisation vermittelten Inhalte auf und setzt diese mit weiterführenden Themen fort. Es werden zunächst grundlegende fortgeschrittene Techniken bei Pipelineverarbeitung und Cachezugriffen in modernen Prozessoren und Parallelrechnern behandelt. Ferner wird die Architektur von Spezialprozessoren, z.B. DSPs und Embedded Prozessoren behandelt. Es wird aufgezeigt, wie diese Techniken in konkreten Architekturen (Intel Nehalem, GPGPU, Cell BE, TMS320 DSP, Embedded Prozessor ZPU) verwendet werden. Zur Vorlesung werden eine Tafel- und eine Rechnerübung angeboten, durch deren erfolgreiche Beteiligung abgestuft mit der Vorlesung 5 bzw. 7,5 ECTS erworben werden können. In den Tafelübungen werden die in der Vorlesung vermittelten Techniken durch zu lösende Aufgaben vertieft. In der Rechnerübung soll u.a. ein einfacher Vielkern-Prozessor auf Basis des ZPU-Prozessors mit Simulationswerkzeugen aufgebaut werden. Im Einzelnen werden folgende Themen behandelt:

-

Organisationsaspekte von CISC und RISC-Prozessoren

-

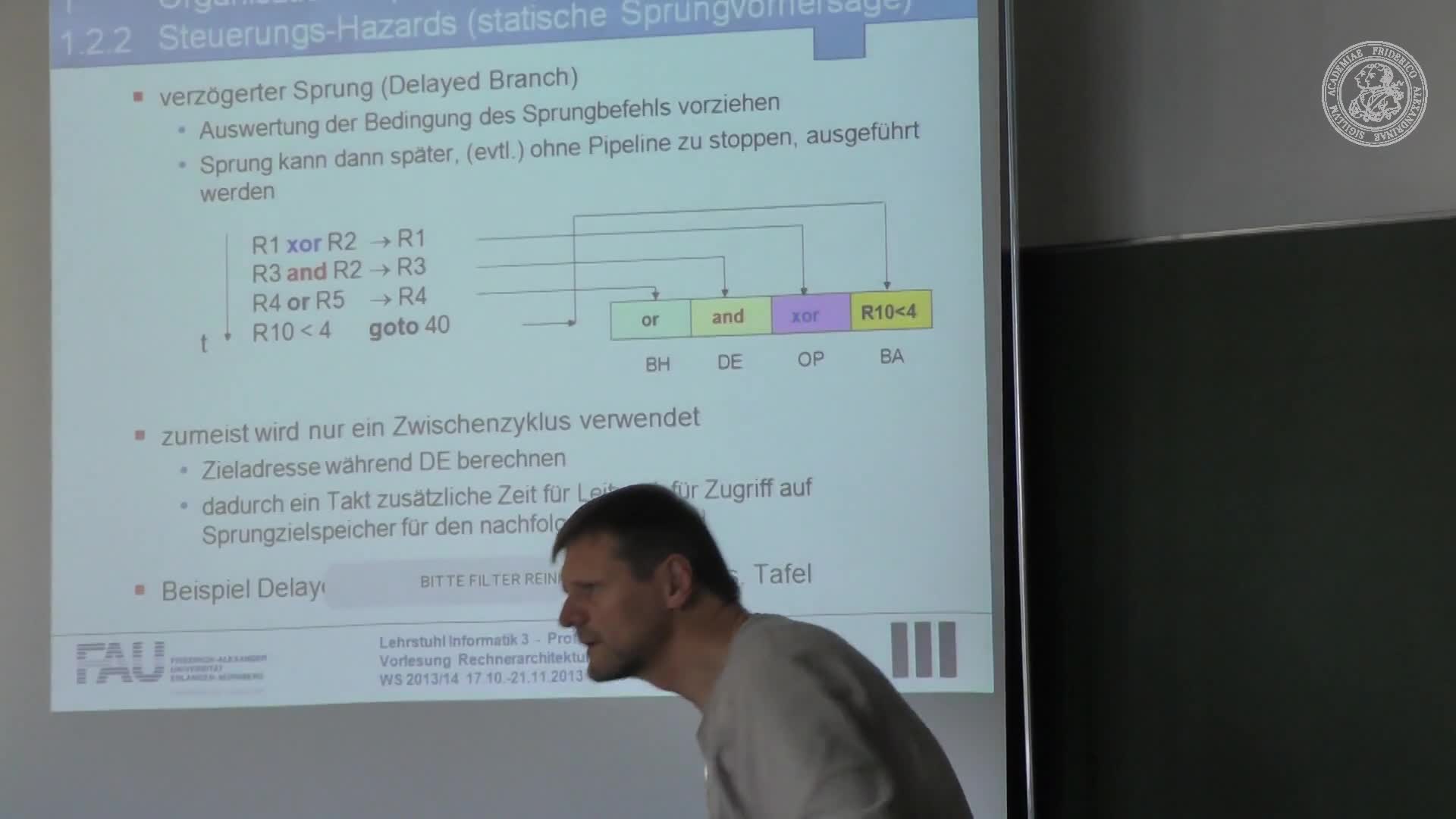

Behandlung von Hazards in Pipelines

-

Fortgeschrittene Techniken der dynamischen Sprungvorhersage

-

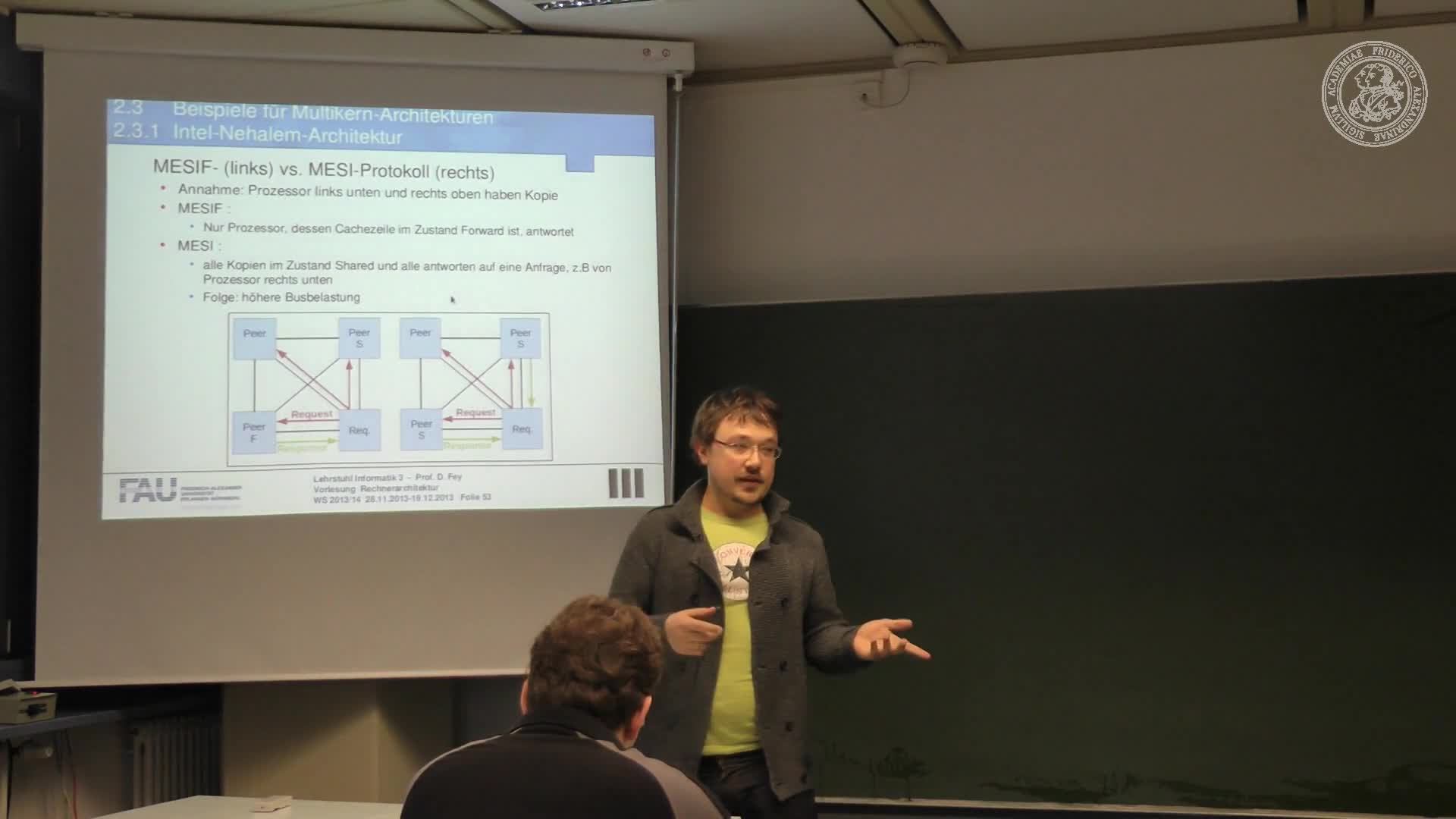

Fortgeschritten Cachetechniken, Cache-Kohärenz

-

Ausnutzen von Cacheeffekten

-

Architekturen von Digitalen Signalprozessoren

-

Architekturen homogener und heterogener Multikern-Prozessoren (Intel Corei7, Nvidia GPUs, Cell BE)

-

Architektur von Parallelrechnern (Clusterrechner, Superrechner)

-

Effiziente Hardware-nahe Programmierung von Mulitkern-Prozessoren (OpenMP, SSE, CUDA, OpenCL)

-

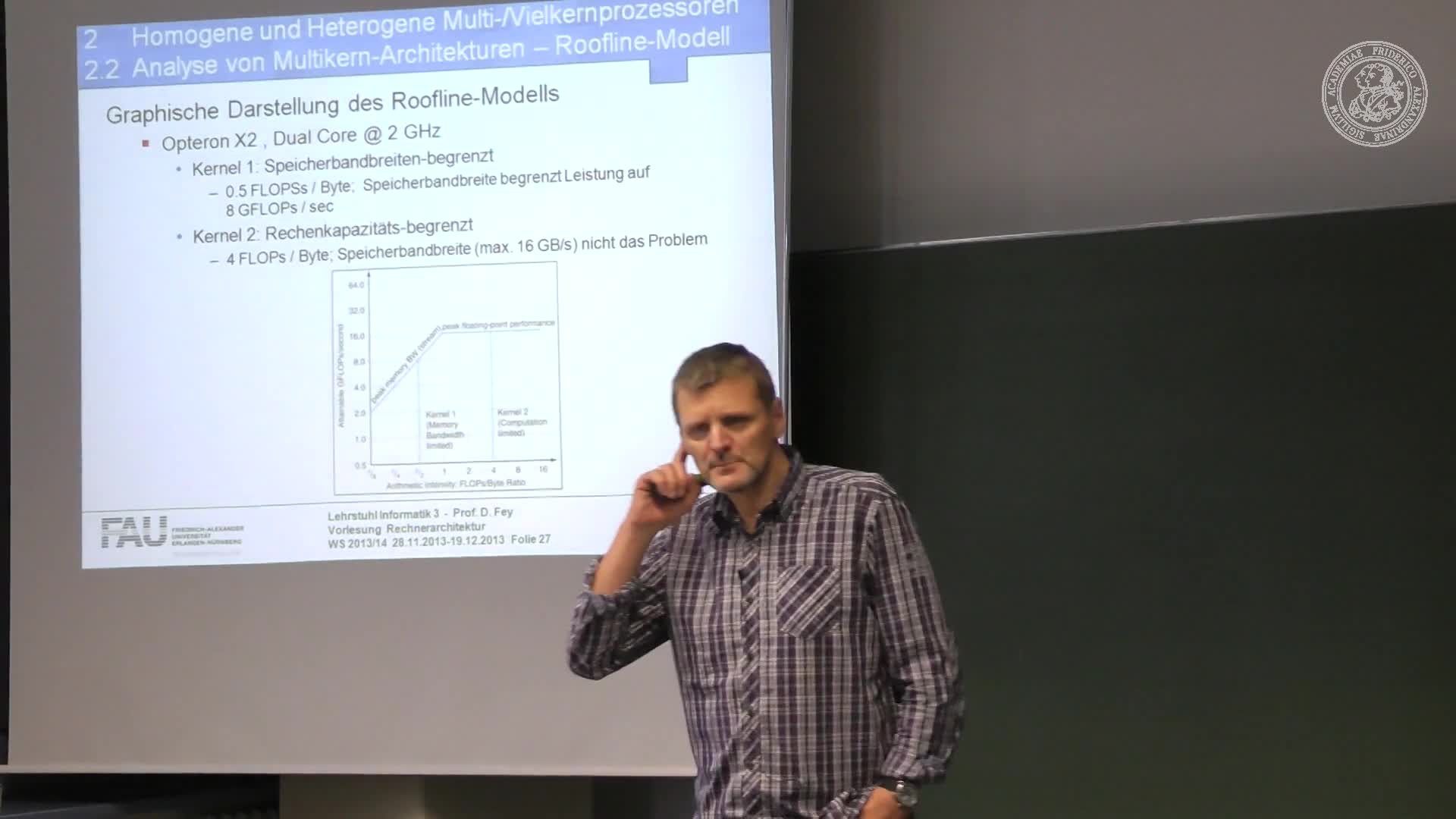

Leistungsmodellierung und -analyse von Multikern-Prozessoren (Roofline-Modell)

-

- Empfohlene Literatur

-

- Patterson/Hennessy: Computer Organization und Design

-

Hennessy/Patterson: Computer Architecture - A Quantitative Approach

-

Stallings: Computer Organization and Architecture

-

Märtin: Rechnerarchitekturen

Rechnerarchitektur 2013/2014 /KursID:791

- Letzter Beitrag vom 2013-12-19

Zugehörige Einzelbeiträge

Folge

Titel

Lehrende(r)

Aktualisiert

Zugang

Dauer

Medien

1

Rechnerarchitektur

Prof. Dr. Dietmar Fey

2013-10-17

Frei

01:31:56

Folien

Audio

captions

2

Rechnerarchitektur

Prof. Dr. Dietmar Fey

2013-10-24

Frei

01:26:37

Folien

Audio

captions

3

Rechnerarchitektur

Prof. Dr. Dietmar Fey

2013-10-31

Frei

01:28:25

Folien

Audio

captions

4

Rechnerarchitektur

Prof. Dr. Dietmar Fey

2013-11-07

Frei

01:32:33

Folien

Audio

captions

5

Rechnerarchitektur

Prof. Dr. Dietmar Fey

2013-11-14

Frei

01:35:19

Folien

Audio

captions

6

Rechnerarchitektur

Prof. Dr. Dietmar Fey

2013-11-21

Frei

01:32:16

Folien

Audio

captions

7

Rechnerarchitektur

Prof. Dr. Dietmar Fey

2013-11-28

Frei

01:31:18

Folien

Audio

captions

8

Rechnerarchitektur

Prof. Dr. Dietmar Fey

2013-12-05

Frei

01:27:08

Folien

Audio

captions

9

Rechnerarchitektur

Prof. Dr. Dietmar Fey

2013-12-12

Frei

01:40:09

Folien

Audio

captions

10

Rechnerarchitektur

Prof. Dr. Dietmar Fey

2013-12-19

Frei

01:32:09

Folien

Audio

captions

11

Rechnerarchitektur

Prof. Dr. Dietmar Fey

2013-01-09

Frei

01:29:10

Folien

Audio

captions

12

Rechnerarchitektur

Prof. Dr. Dietmar Fey

2013-01-16

Frei

01:29:02

Folien

Audio

captions

13

Rechnerarchitektur

Prof. Dr. Dietmar Fey

2013-01-30

Frei

01:03:07

Folien

Audio

captions

14

Rechnerarchitektur

Prof. Dr. Dietmar Fey

2013-02-06

Frei

01:19:05

Folien

Audio

captions

Mehr Kurse von Prof. Dr. Dietmar Fey

Prof. Dr. Dietmar Fey

Vorlesung

2017-07-25

IdM-Anmeldung

Prof. Dr. Dietmar Fey

Vorlesung

2022-01-24

IdM-Anmeldung

Prof. Dr. Dietmar Fey

Vorlesung

2024-02-06

IdM-Anmeldung

Prof. Dr. Dietmar Fey

Vorlesung

2022-09-23

Studon

Prof. Dr. Dietmar Fey

Vorlesung

2018-07-09

Frei

Mehr Kurse aus der Kategorie "Technische Fakultät"

M. Sc. Dominic Soldner

Übung

2019-07-22

IdM-Anmeldung

Prof. Dr. Stefan Milius

Vorlesung

2016-07-13

IdM-Anmeldung

M. Sc. Michael Jüttner

Übung

2022-02-09

Studon

Prof. Dr. Andreas Maier

Vorlesung

2016-11-08

Studon

Prof. Dr. Stefan Becker

Vorlesung

2021-02-12

Studon